Vertex Forms an Illegal Shape Select Again Orcad Pcb

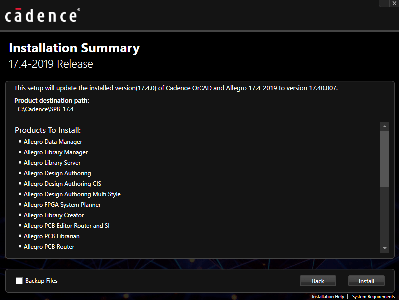

Cadency SPB Allegro and OrCAD 17.40.000-2019 QIR1 (HotFix 007) | 4.eight Gb

Cadence Design Systems, Inc. , the leader in global electronic design innovation, has unveiled a new of improvements in hot fix 007 to the Cadence SPB Allegro and OrCAD 17.40 families of products aimed at boosting performance and productivity through improvements features and big fixed issues.

Cadence OrCAD and Allegro: What'southward New in 17.4-2019 QIR1 (HotFix 007)

This document describes the new features and enhancements in Cadence Allegro and OrCAD products in release 17.4-2019, Quarterly Incremental Release (QIR) one.

=====================================================================================

CCRID Production ProductLevel2 Title

=====================================================================================

2247686 ADW Cadre Allegro EDM: Unable to create a project using a newly created menstruum

2137594 ADW DBADMIN EDM is not allowing changes to STEP models

2135452 ADW DBEDITOR DBEditor poor performance in high-latency networks

2113265 ADW LIBDISTRIBUTI Various database operations take a long time; rebooting server seems to set the trouble

2122941 ADW LIBDISTRIBUTI Lib_dist execution taking a long time to run; Capture CIS DBC file appears to be taking the near time

2127319 ADW LIBDISTRIBUTI Library distribution fails at cisexport function with error (ORCIS-6250)

1975317 ADW PART_BROWSER Space at the end of the line in CDS.LIB results in zero libraries being shown in System Capture library search

2078057 ADW PART_BROWSER Symbol Graphics preview is not bachelor in Designer Servers

2092863 ADW PART_BROWSER Organisation Capture library search is not displaying the symbol and footprint preview

2086463 ADW PART_MANAGER Organization Capture cannot add components when accessing remote auto via Citrix

2092868 ADW PART_MANAGER Release 17.2-2016, HotFix 054: Empty cache.ptf causing injected backdrop to not menstruation from pstchip

2092872 ADW PART_MANAGER Organisation Capture stops responding when importing from DE-HDL

2113226 ADW PART_MANAGER System Capture stops responding while importing DE-HDL sheets

2212406 ADW PART_MANAGER Allegro Organisation Capture: Function Manager is deleting properties from all instances upon Update

2025147 ADW TDO-SHAREPOIN Pattern Management stops responding when a board file is deleted and and so checked in with the same name

2025201 ADW TDO-SHAREPOIN Getting mistake message (SPDWSD-20) when logging in to Team Design

2056694 ADW TDO-SHAREPOIN Pattern Management stops responding on checking in an object with the same name equally a previously deleted object

2048086 ALLEGRO_EDITOR 3D_CANVAS Wire bonds are not linked to die pad when component is embedded trunk down

2051277 ALLEGRO_EDITOR 3D_CANVAS Vias are commencement from board in Z direction in 3D Sheet

2054243 ALLEGRO_EDITOR 3D_CANVAS Plating is not shown on stacked vias in 3D canvas

2054327 ALLEGRO_EDITOR 3D_CANVAS 3D Sail error: All bend operations are disabled due to licensing and/or DLL installation

2079732 ALLEGRO_EDITOR 3D_CANVAS Enhance 3D Canvas to merge the lines segment and overlapping lines and shapes

2206045 ALLEGRO_EDITOR ARTWORK Artwork Control Course fails to create film if Film record has a menstruation (.) in the title

2209200 ALLEGRO_EDITOR ARTWORK PCB Editor stops responding on rebuilding apertures without rotation

2244407 ALLEGRO_EDITOR ARTWORK Automated editing apertures with rotation takes fourth dimension in the General Parameters tab of Artwork Command Form

2267942 ALLEGRO_EDITOR ARTWORK Allegro PCB Editor stops responding when generating apertures in HotFix 006

567342 ALLEGRO_EDITOR Colour Add option under View menu for 'load color view'

637828 ALLEGRO_EDITOR Colour Line highlights in 'shape select' control

720274 ALLEGRO_EDITOR COLOR Add menu selection for the 'colorview load' command

1602652 ALLEGRO_EDITOR Color Color/Visibility behavior variation using "Enable Layer Select Mode"

2072695 ALLEGRO_EDITOR COLOR Clines of colored nets not colored when 'display_nohighlight_priority' is set

2207580 ALLEGRO_EDITOR COLOR Component color is inconsistent when display_nocolor_dynamics is gear up.

2056497 ALLEGRO_EDITOR DATABASE Place transmission is deadening

2250988 ALLEGRO_EDITOR DATABASE Inner Layer keep out equally illegal subclasses: Shape object may not exist on layer ROUTE KEEPOUT/INNER_SIGNAL_LAYERS

2096958 ALLEGRO_EDITOR DFA Cannot launch Constraint Director later assigning CSet and closing

2049681 ALLEGRO_EDITOR DFM DFF cheque for plating in via should not flag DRC for surface mount testpoint Via

2155060 ALLEGRO_EDITOR DFM Inconsistent behavior in displaying DRCs for Via to Via spacing

2166431 ALLEGRO_EDITOR DFM DesignTrue annular ring thru pin pad to mask checks compared to smd pin to mask checks are inconsistent in behavior

2221975 ALLEGRO_EDITOR DFM DFM missing mask check reporting mask is missing when pins have a mask geometry overlaying them.

2249498 ALLEGRO_EDITOR DRAFTING When a Symbol with a Dimension is placed on the lath, an actress Dimension is added to the Symbol origin.

2250631 ALLEGRO_EDITOR DRC_CONSTR Cannot import netlist into blueprint due to illegal DRC chemical element: no DBDoctor mistake

1794593 ALLEGRO_EDITOR EDIT_ETCH Unable to deselect render path vias selected when creating High-speed via structures

2099538 ALLEGRO_EDITOR EDIT_ETCH Gloss - Via Eliminate shifts traces to another layer

2204339 ALLEGRO_EDITOR EDIT_ETCH Differential pair line lost during slide operation

2208938 ALLEGRO_EDITOR EDIT_ETCH Slide operation makes one of the differential pair cline invisible

2222047 ALLEGRO_EDITOR EDIT_ETCH One of the traces disappear when sliding a differential pair in unmarried trace way

2233991 ALLEGRO_EDITOR EDIT_ETCH 1 cline of a differential pair disappears temporarily upon sliding the Differential Pair in Single Trace Mode

2240827 ALLEGRO_EDITOR EDIT_ETCH Cline of a Differential pair net disappears later on sliding the other internet of the Differential pair

2245775 ALLEGRO_EDITOR EDIT_ETCH Differential pair slide in single trace style removes other trace

1813358 ALLEGRO_EDITOR GRAPHICS Allegro PCB Editor enables shape boundary when disabling etch layer in Visibility pane

1911613 ALLEGRO_EDITOR GRAPHICS The subclass for purlieus class stays on, fifty-fifty if Bracket for Etch Class is turned off from Visibility tab

1966343 ALLEGRO_EDITOR GRAPHICS Shape boundary remains enabled even after turning off the etch layer visibility

2195276 ALLEGRO_EDITOR GRAPHICS Selecting File view is slow

2031883 ALLEGRO_EDITOR INTERACTIV Sub-Drawing: Clipboard origin point is not set correctly

2050177 ALLEGRO_EDITOR INTERACTIV Messages demand to remain aligned and compatible subsequently performing Shape ANDNOT operation

2069247 ALLEGRO_EDITOR INTERACTIV DFA bubble on wrong layer after mirroring the function

2103711 ALLEGRO_EDITOR INTERACTIV Placement edit mode popup 'Rotate' leaves ghost image in the background

2136859 ALLEGRO_EDITOR INTERACTIV DFA Problem if we mirror component while placing

2165027 ALLEGRO_EDITOR INTERACTIV Different behavior in OrCAD Capture when using crossprobe to select Power nets

2240235 ALLEGRO_EDITOR INTERACTIV The blueprint file proper noun changes automatically to board template proper noun while creating new lath (wizard).

2244765 ALLEGRO_EDITOR INTERACTIV License 4150+226 does not accept AiDT/AiPT in release 17.two-2016

2259800 ALLEGRO_EDITOR INTERACTIV DFA DRC circle not shown on the layer of placement in Placement App Mode

2120420 ALLEGRO_EDITOR INTERFACES Drill figures missing in the exported PDF if drill fable deleted

2136454 ALLEGRO_EDITOR INTERFACES Export - PDF output is non correct

2116748 ALLEGRO_EDITOR IN_DESIGN_ANA Impedance vision data not available for cline segments for some nets

2138977 ALLEGRO_EDITOR IN_DESIGN_ANA Impedance check results are incorrect and Crosstalk analysis stops running after updating to 17.2-2016, HotFix 057

2247167 ALLEGRO_EDITOR IN_DESIGN_ANA IDA Impedance Analysis: Add an option to export CSV automatically

2222638 ALLEGRO_EDITOR IPC Documentation Editor crashes with error: Failed to complete the job because of unspecified fault

2106425 ALLEGRO_EDITOR NC Disable undersize regular pad and oversize soldermask pad for beginning layers in Backdrill Setup and Analysis

2091932 ALLEGRO_EDITOR OTHER Unsupported Prototypes command missing for the OrCAD licenses

2221345 ALLEGRO_EDITOR OTHER Speed up Allegro PCB Editor startup by removing bank check for defunct PCB/Package co-design capability (NG_450)

2257934 ALLEGRO_EDITOR PLACEMENT Mistake (SPMHGE-626) on place component: Symbol not valid on any layer

1001000 ALLEGRO_EDITOR PLOTTING File - Plot in PCB Editor does not plot more than one copy

2234538 ALLEGRO_EDITOR REPORTS Allow Unused Blind/Cached Via written report to run equally Batch Procedure through the reports batch command

2222738 ALLEGRO_EDITOR SCHEM_FTB Netrev not completing, showing mistake for electric constraints data (pstcmdb.dat) import

2255426 ALLEGRO_EDITOR SCHEM_FTB Netrev is running for hours without closing

1702190 ALLEGRO_EDITOR SCRIPTS Allegro PCB Editor script file: Some sub-classes not created and mistake for form field label

1791099 ALLEGRO_EDITOR SCRIPTS Allegro PCB Editor does not terminate when the script is run with '-nographic'

1791267 ALLEGRO_EDITOR SCRIPTS Allegro PCB Editor script does not run with '-nograph' in release 17.2-2016

1892520 ALLEGRO_EDITOR SCRIPTS Allegro PCB Editor stops responding for script when run with '-nographic'

1962010 ALLEGRO_EDITOR SCRIPTS Allegro PCB Editor stops responding for script when run with -nongraph option

2056857 ALLEGRO_EDITOR SHAPE Shape boundary error past shape parameter

2081946 ALLEGRO_EDITOR SHAPE Shape Update takes twice the fourth dimension in release 17.two-2016, HotFix 053 as compared to HotFix 047

2104559 ALLEGRO_EDITOR SHAPE PCB Editor crashes while performing shape performance 'andnot'

2108207 ALLEGRO_EDITOR SHAPE No Void Overlap pick is not working in Auto Metal Balancing (AMB)

2240996 ALLEGRO_EDITOR SHAPE Detecting Shape Island: Ignored for copied or moved shape

2258758 ALLEGRO_EDITOR SHAPE Allegro PCB Editor crashes when routing two signals together

717389 ALLEGRO_EDITOR SKILL Ability to set and render the application mode using SKILL

853160 ALLEGRO_EDITOR SKILL Need ability to get and gear up application modes using SKILL

981446 ALLEGRO_EDITOR SKILL Request the ability to get and prepare application modes using SKILL

1235409 ALLEGRO_EDITOR SKILL SKILL choice to get application mode

1316962 ALLEGRO_EDITOR SKILL SKILL option to switch between application modes

1553621 ALLEGRO_EDITOR SKILL Ability to modify application modes using SKILL function

1885442 ALLEGRO_EDITOR SKILL Power to modify awarding modes using SKILL function.

2080351 ALLEGRO_EDITOR SKILL SKILL to determine current application mode

2195645 ALLEGRO_EDITOR THIEVING Thieving pad cannot be added on some areas in the board in latest hotfix but could be added before

1721594 ALLEGRO_EDITOR UI_FORMS STEP name Filter for Stride Packet mapping form should be instance insensitive

2090604 ALLEGRO_EDITOR UI_FORMS Undo/Redo UI grayed out when invoking Color192

2203278 ALLEGRO_EDITOR UI_FORMS 'Width' keyword in Place Rectangle field is grayed out when Place Rectangle is selected

2209172 ALLEGRO_EDITOR UI_FORMS Labels truncated by drop-down lists in Options ('Industry' - 'Drafting' - 'Relative Copy')

2239426 ALLEGRO_EDITOR UI_FORMS Cannot start text size with decimal in 'Design Parameter Editor' - 'Text' for English (Denmark) regional settings

2245035 ALLEGRO_EDITOR UI_FORMS The right edge of the default Define Grid grade looks cut off in 17.iv.

2245955 ALLEGRO_EDITOR UI_FORMS Resizing of 'Turn down Item Selection' window not possible in release 17.4-2019, HotFix 004

2249202 ALLEGRO_EDITOR UI_FORMS Extra click required to activate Laissez passer field in Autorouter class

2259605 ALLEGRO_EDITOR UI_FORMS Add ability to resize Refuse pop-up

2090517 ALLEGRO_EDITOR UI_GENERAL Shape visibility box is not being enabled with the Enable layer select manner option in the Visibility Pane

2092436 ALLEGRO_EDITOR UI_GENERAL RefDes length of input string for Modify Pattern Padstack is limited to 20 characters

2134781 ALLEGRO_EDITOR UI_GENERAL The Pivot Grade is missing in Options tab when creating or opening a Mechanical Symbol

2168026 ALLEGRO_EDITOR UI_GENERAL Edit Properties UI slow to launch for boards with many drawing properties

2191267 ALLEGRO_EDITOR UI_GENERAL Irresolute Visibility of any object type disables links in Layer Select Mode in the Visibility pane

2208018 ALLEGRO_EDITOR UI_GENERAL Text on BGA pins not visible in release 17.iv-2019 if not zoomed to maximum

2225753 ALLEGRO_EDITOR UI_GENERAL night theme does not respect TRBICON size for 4K monitors

2256841 ALLEGRO_EDITOR UI_GENERAL Enlarge the Shape Copy to Layers form equally the window is quite minor and not resizable

2258019 ALLEGRO_EDITOR UI_GENERAL Canvas turns white subsequently endmost STEP Parcel Mapping window

2258167 ALLEGRO_EDITOR UI_GENERAL Heighten 'Shape copy to layers' window in release 17.4-2019 to expand or resize

2262305 ALLEGRO_EDITOR UI_GENERAL Assign Differential Pair grade listing box size too small to add together signals

2086574 APD OTHER APD is showing duplicate layer text on the vias

1723825 APD SCRIPTS Allegro Package Designer in release 17.2 is not writing out to either jrl files or script files in real time.

2186363 APD UI_GENERAL Text on the Pivot is non visible until zoomed in to certain extent

2253484 APD WIREBOND APD stops responding when running 'wirebond soldermask create' with 'Measure from soldermask pad'

2241725 CAPTURE DRC Waive DRC option not working from batch DRC window

2243645 CAPTURE DRC Online DRC bug in release 17.four-2019, hotfix 004 - offpage connector does not take wire

2250867 CAPTURE DRC Hanging wire custom DRC not working when selected standalone

2252912 CAPTURE DRC Unable to create new DRC file using Browse button in DRC window

2047391 CAPTURE PART_EDITOR Pivot type cannot be inverse in release 17.two-2016, hotfix 051

2183187 CAPTURE SCHEMATIC_EDI OrCAD Capture: Ctrl + Due north seems to call a legacy dialog that allows projects to be created with no proper name

2190602 CAPTURE SCHEMATIC_EDI Cascading options of Window card non working in OrCAD Capture in release 17.iv-2019

2194374 CAPTURE UX Design Sync bug: Session log does not report information about errors

2183037 CIS LINK_DATABASE CTRL-50 shortcut for Link DB-Parts for Query in CIS-Explorer non working

2201323 CIS PLACE_DATABAS Capture CIS displays empty dialog on placing office from database in release 17.4-2019

2216963 CIS PLACE_DATABAS Lite Theme: Alert text not visible in Capture CIS dialog

2246354 CIS PLACE_DATABAS Warning (ORCIS-6159) pop-up window is blank.

2230651 CONCEPT_HDL CHECKPLUS Discrepancy in the 'checkplus' marking files

2237145 CONCEPT_HDL CONSTRAINT_MG T-Points match groups get deleted after saving a design

2246452 CONCEPT_HDL Cadre Folio data gets removed from 'chief.tag' of the superlative-level design when subdesigns are read-only

2057490 CONSTRAINT_MGR CONCEPT_HDL Constraint Manager Worksheet flips afterward running hier_write when CM is open up

2236329 CONSTRAINT_MGR CONCEPT_HDL Pin Pairs non added to Match Group

2214367 CONSTRAINT_MGR INTERACTIV CSet assignment matrix sorting in Net Class-class random in Capture to Constraint Managing director menstruation

2243574 CONSTRAINT_MGR OTHER CM SKILL cmxlPutAttribute() cannot set constraint value

2259598 CONSTRAINT_MGR OTHER Importing netlist: Mistake for electric constraint data (pstcmdb.dat) import

2207862 CONSTRAINT_MGR SYSCAP Relieve icon and 'File' - 'Save' carte in Constraint Director is inactive

2200316 CONSTRAINT_MGR UI_FORMS Expanding 'Analysis Manner' form resets cavalcade width

2097479 PCB_LIBRARIAN Core Symbol import in Part Developer does not show the correct pin shape.

2145385 PCB_LIBRARIAN Core Error-SPLBPD-972 reports missing parentheses in the ALT_SYMBOLS belongings of a part

2202622 PCB_LIBRARIAN Cadre When calculation a new pivot to a symbol in Symbol Editor, the space between pins changes

1955570 PCB_LIBRARIAN FLOW Using the PACK_SHORT belongings with more than 256 characters does not piece of work or report an error on packaging

2072190 PCB_LIBRARIAN Catamenia Permit PACK_SHORT belongings value longer than 255 characters

1720395 PCB_LIBRARIAN IMPORT_OTHER Converting OrCAD Capture OLB to Design Entry HDL library adds braces to pin number

2141340 PCB_LIBRARIAN SETUP SPLBPD-216 Mistake logged in PDV even when MAX_SIZE Sheet is divers

2214973 PCB_LIBRARIAN SETUP Unable to apply symbol holding templates when PDV lock directives are set

2257527 PCB_LIBRARIAN SETUP Locking PDV directives prevents applying symbol property templates

2033898 PCB_LIBRARIAN SYMBOL_EDITOR Running Symbol Editor with no arguments results in a groundwork process, non an error.

2093849 PCB_LIBRARIAN SYMBOL_EDITOR Symbols and font sizes appear different when placed in designs

2200399 PCB_LIBRARIAN SYMBOL_EDITOR Multiple problems observed when editing parts in the New Symbol Editor

2218940 PCB_LIBRARIAN SYMBOL_EDITOR Indistinguishable pins cannot be removed

2230542 PCB_LIBRARIAN SYMBOL_EDITOR Jitney pin location changes after expanding or collapsing pins in Symbol Editor

2239303 PCB_LIBRARIAN SYMBOL_EDITOR Expanding and collapsing a passenger vehicle is changing the msb and lsb for the pin name

2243431 PCB_LIBRARIAN SYMBOL_EDITOR Grouping of pins that are not adjacent cannot be moved together

2029056 PCB_LIBRARIAN SYMBOL_EDITOR Unable to change Grid Settings in Part Developer

2149948 PCB_LIBRARIAN SYMBOL_EDITOR New Symbol Editor and System Capture moved pins from 0.01 grid to 0.05 filigree.

2206975 PSPICE MODELEDITOR PSpice Model Import Magician symbol preview readability improvement requested

2211187 PSPICE MODELEDITOR Model Editor color scheme non readable

2214415 PSPICE MODELEDITOR Symbol view in Model Import Wizard has a visibility trouble

2199570 PSPICE PROBE Unable to 'select sections' after Monte Carlo runs with Temperature

2244140 PSPICE PROBE Not able to select multiple sections to plot in probe

2249565 PSPICE PROBE Selecting multiple traces for PSpice A/D Monte Carlo run not working

2171626 PULSE CORE Pulse crashed with error related to tertiary-party evolution kit platform issue

2221523 PULSE UNIFIED_SEARC Cannot log in to 3rd-party search providers only tin can log in to Cadence Online Support

2019229 RF_PCB OTHER Layer conversion file data does not update GDSII layer mapping using Package Symbol Wizard

820288 SIP_LAYOUT Colour Layer Priority command does not seem to exist functioning

820305 SIP_LAYOUT Color Layer Priority menus practice non match the Color dialog in the package substrate tools

2256044 SIP_LAYOUT DATABASE Fix teardrop does not piece of work for some situation: Deleting fixed fillets

2254932 SIP_LAYOUT DEGASSING APD Plus generating assertion failures when running degassing manner with script

2106314 SIP_LAYOUT INTERACTIVE Large design causing severe lag in Windows Server machine

2096239 SIP_LAYOUT STREAM_IF Database fails to create stream out file

2079071 SIP_LAYOUT SYMB_EDIT_APP Response very tedious afterward Testify IC Details on a very large co-design die

2251630 SIP_LAYOUT WIREBOND 'Change Contour' does not change the diameter of the wire bond

2253633 SIP_LAYOUT WLP Advanced degassing passing illegal arguments to dba routine

2259630 SIP_LAYOUT WLP Avant-garde WLP: Import PVS DRC results in mistake

1968437 SYSTEM_CAPTURE ASSIGN_SIGNAL Net name pasted in lower-example though majuscule input is enabled

2131976 SYSTEM_CAPTURE AUTOMATION syscap exits when run with the -tclfile argument and an invalid Tcl file

1983063 SYSTEM_CAPTURE BLKDIAGRAM_AU Auto Shapes are beingness shown as part of components

1977673 SYSTEM_CAPTURE COMPONENT_BRO adding reference blocks through add component error when jail cell name matches design name

2247567 SYSTEM_CAPTURE COMPONENT_BRO Symbol property placeholder changes not updated on the canvas

2027100 SYSTEM_CAPTURE COMPOSITE_FIL pstdedb.cdsz and netlist preview in Arrangement Capture is not being updated when individual netlist files are written

1863460 SYSTEM_CAPTURE DARK_THEME thumbnail preview of pages is in light them merely dragging the page the previes is night

2168622 SYSTEM_CAPTURE EDIT_SEARCHRE Reports from Notice Results are dumped fifty-fifty when the performance is canceled

2168625 SYSTEM_CAPTURE EDIT_SEARCHRE Sort icons for columns in 'Find Results' are incorrectly placed: appear to be in side by side column

1895142 SYSTEM_CAPTURE EXPORT_PCB System Capture incorrectly reports unsaved changes when closing later on running consign physical

1931660 SYSTEM_CAPTURE EXPORT_PCB SDA is not-responsive while Allegro launches and opens a board when launched from SDA

2087387 SYSTEM_CAPTURE EXPORT_PCB System Capture: After Export PCB completes, decorated cursor shown for a while

2202179 SYSTEM_CAPTURE FIND_REPLACE Replacing a net proper noun with the same name by using Notice and Replace results in a crash

1843885 SYSTEM_CAPTURE FORMAT_OBJECT Renaming a net causes it to lose custom color consignment

1993208 SYSTEM_CAPTURE FORMAT_OBJECT Setting font prior to placing text does not piece of work, popular-up does not work, and bucket results in scrolling page

2231399 SYSTEM_CAPTURE IMPORT_BLOCK 'importBlock' Tcl control non working when using a script

1907729 SYSTEM_CAPTURE IMPORT_DEHDL_ Import DE-HDL sheets - differential pair properties on nets are lost

2025949 SYSTEM_CAPTURE IMPORT_DEHDL_ Title cake and thick wires/lines of border in DE-HDL do non translate in System Capture

1942542 SYSTEM_CAPTURE IMPORT_PCB System Capture - TDO backannotation overwrites net names with stale data in lower-level blocks

1982320 SYSTEM_CAPTURE IMPORT_PCB View files are not created in the schematic-to-board menstruation

2117532 SYSTEM_CAPTURE MENUS_AND_TOO Ability to customize menus for a site

2213478 SYSTEM_CAPTURE MENUS_AND_TOO Help - About menu item appears twice

1910941 SYSTEM_CAPTURE MISCELLANEOUS Parts that are not in any schematic folio appear in netlist and BOM

1967614 SYSTEM_CAPTURE MISCELLANEOUS Dragging a circuit with net aliases does not motility the net aliases with it

2189846 SYSTEM_CAPTURE MISCELLANEOUS Inconsistent display of same font

2178961 SYSTEM_CAPTURE NOTES Cannot add Japanese text in notes in release 17.4-2019 on Windows 10

1973437 SYSTEM_CAPTURE OPEN_CLOSE_PR Opening a design crashes System Capture

2079857 SYSTEM_CAPTURE OPEN_CLOSE_PR System Capture: Unable to select design to open if license selection box is canceled the first time

2065025 SYSTEM_CAPTURE PACKAGER Export to PCB Layout reports wrong path but exports correctly

2229611 SYSTEM_CAPTURE PACKAGER Path for the 'packaged' folder shown in the 'Export Physical' is wrong

1993146 SYSTEM_CAPTURE PROJECT_EXPLO Cannot movement page upwards by but one position

1892120 SYSTEM_CAPTURE PROPERTY_EDIT Some parts are missing reference designators and some accept ii properties - RefDes and REFDES

2201060 SYSTEM_CAPTURE PROPERTY_EDIT Some of the icons in the Backdrop window practice not have tooltips

2246667 SYSTEM_CAPTURE SCRIPTING Running the 'replay.tcl' script gives an invalid command name error

2010032 SYSTEM_CAPTURE SHORTCUTS Cannot enter Folio-Up/Page-Down every bit shortcuts

2017985 SYSTEM_CAPTURE TDO Allegro System Capture ability for multiple users to open a blueprint

2106743 SYSTEM_CAPTURE TDO Ability for multi-user access to the same schematic

2209628 SYSTEM_CAPTURE UI Tooltips for Blueprint Rule Checks are getting truncated

1990258 SYSTEM_CAPTURE VARIANT_MANAG Cannot paste copied preferred part to multiple parts with the aforementioned part number

2032005 SYSTEM_CAPTURE VARIANT_MANAG Custom variables not saved for variants

2228299 SYSTEM_CAPTURE VARIANT_MANAG CAP parts should not show up in the Preferred Parts list when irresolute a RES

1627835 SYSTEM_CAPTURE WIRING Inconsistencies in wire movements

1670888 SYSTEM_CAPTURE WIRING Rotation error when a component is connected to a power symbol

1721863 SYSTEM_CAPTURE WIRING Net names move to random locations when components are moved around the canvas.

1960130 SYSTEM_CAPTURE WIRING Asunder nets when using the mirror option

1961274 SYSTEM_CAPTURE WIRING XNet removed during pin swapping

1968463 SYSTEM_CAPTURE WIRING System Capture should non let illegal characters to exist entered for net names

1973426 SYSTEM_CAPTURE WIRING Selecting multiple net names and trying to delete only deletes one net name.

1978381 SYSTEM_CAPTURE WIRING 'oops' does non remove the first vertex placed

1985029 SYSTEM_CAPTURE WIRING Net aliases are not dragged with circuit, they appear to move after the excursion is dropped

2013647 SYSTEM_CAPTURE WIRING Replacing a vertically oriented RES with a horizontal CAP breaks the wire connections

2014188 SYSTEM_CAPTURE WIRING Context card not working in Variant way

2041879 SYSTEM_CAPTURE WIRING XNets generated for nets with pull-up resistors

2050533 SYSTEM_CAPTURE WIRING Need an choice to increment junction dot size

2061877 SYSTEM_CAPTURE WIRING Unable to add a power symbol with the Place - Special Symbol carte du jour

2079409 SYSTEM_CAPTURE WIRING Increment the size of the wire connection dot in System Capture

2081884 SYSTEM_CAPTURE WIRING Symbols take a long time to move, and results in DRCs and broken connections

2085263 SYSTEM_CAPTURE WIRING System Capture: Focus lost from the Format tab if font name starting with typed letter is not present

2089569 SYSTEM_CAPTURE WIRING Ability to specify the solder dot radius size

Cadence OrCAD and Allegro 17.4-2019 is a sleeker and more modern version of the OrCAD and Allegro release, with enhanced usability and a slew of new productivity- enhancing features. You go more intuitive and easy- to- use flows that enable optimized schematic- to- board- to- manufacturing transitions. So, whether y'all design schematics, work with physical layouts, manage or create libraries and parts, or administer ECAD processes, there are features in this release that will benefit you.

Starting with OrCAD and Cadence Allegro PCB - Tutorial for Beginners

Cadence enables global electronic pattern innovation and plays an essential function in the creation of today's integrated circuits and electronics. Customers utilize Cadency software, hardware, IP and services to pattern and verify avant-garde semiconductors, consumer electronics, networking and telecommunications equipment, and computer systems. The visitor is headquartered in San Jose, Calif., with sales offices, design centers and enquiry facilities around the world to serve the global electronics industry.

Production: Cadence SPB Allegro and OrCAD

Version: 17.40.000-2019 QIR1 (HotFix 007)

Supported Architectures: x64

Website Home Page : world wide web.cadency.com

Language: english

Arrangement Requirements: PC *

Supported Operating Systems: *

Software Prerequisites: Cadence SPB Allegro and OrCAD 17.40.000-2019 and higher up

Size: four.8 Gb

System Requirements:

Bone: Windows 10 (64-bit) Professional person, Windows Server 2012 (All Service Packs); Windows Server 2012 R2; Windows Server 2016.

CPU: Intel Core i7 4.30 GHz or AMD Ryzen 7 4.30 GHz with at least 4 cores

Memory: 16 GB RAM

Space: 50 GB costless disk space (SSD drive is recommended)

Display: 1920 ten 1200 display resolution with true color (at least 32bit color)

GPU: A dedicated graphics card supporting OpenGL, minimum 2GB (with additional back up for DX11 for 3D Canvas)

Monitors: Dual monitors (For concrete design)

Supported MATLAB Version: R2019A-64Bit (For the PSpice-MATLAB interface)

Cadence SPB Allegro and OrCAD 17.40.000-2019

Please visit my web log

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please

Source: https://avxhm.se/software/Cadence-SPB-Allegro-and-OrCAD-17-40-000-2019-QIR1-HotFix-007.html

0 Response to "Vertex Forms an Illegal Shape Select Again Orcad Pcb"

Postar um comentário